本文翻译自OpenROAD官网提供文献 INVITED: Toward an Open-Source Digital Flow: First Learnings from the OpenROAD Project摘要

我们描述了 OpenROAD 计划中的Alpha版本,这是一个开源端到端的硅编译器 (silicon compiler)。OpenROAD 将通过降低成本、专业技术、和当今系统设计者所面临的风险来实现 “硬件设计民主化” (democratization of hardware design) 的目标。开源的、自驱动的设计工具的开发本身就是一场 “登月”,面临着众多的技术和文化挑战。开源流程包含了一套兼容的开源工具,涵盖了逻辑综合、floorplan、布局、时钟树综合、全局布线和详细布线。该流程还包含用于静态时序分析、寄生参数提取 (parasitic extraction)、电力完整性分析 (power integrity analysis) 和云部署的分析和支持工具。我们也注意到一些与开源EDA工具和流程开发相关的挑战。

1. 导言

尽管硬件设计工具和方法在过去几十年中取得了进步,但半导体行业仍未能控制产品设计成本。今天,成本、专业知识和不可预测性(风险)这些障碍阻碍了设计师使用先进技术实现硬件。换句话说:硬件系统创新受困于 (1) 复杂而昂贵的工具,(2) 缺乏能够在先进技术中使用这些工具的专业用户,(3) 即使是尝试硬件设计,也面临巨大的成本和风险障碍.

特别地,在 IC 领域,布图自动化以高级技术节点的方式,已经集成到巨大的,极其复杂的软件产品当中。然而,设计能力的缺失——例如,伴随底层设备的进步和模式技术的提升,相应地去提高产品质量的能力——在过去的十年里变得明显基于开源工具的数据分析,甚至在一些先进的公司。 因此,为了满足产品和计划的需求,如今的前沿 SoC 产品公司必须将大的设计团队进行划分,每个单独的设计模块交给一个小团队去完成,并且每个团队里的设计者都有对应方面的专业知识。许多开发团队没有足够的资源来执行这样的策略,因此他们的硬件设计周期一般在 12-36 个月。

为了克服上述的限制,跟上摩尔定律下的 SoC 指数级增长的复杂性,DARPA IDEA 计划旨在开发一个全自动的,"no human in the loop" 电路版图生成器,使没有电子设计经验的使用者也能够完成电子硬件的物理设计。OpenROAD("Foundations and Realization of Open, Accessible Design")项目起始于2018年6月,作为 DARPA IDEA 计划的一部分。OpenROAD 的首要目标是减少阻碍系统设计者进行硬件设计的成本,专业知识,高风险行这些障碍。团队的贡献者包括来自 Qualcomm, Arn 和由加州大学圣迭戈分校领导的多所大学。OpenROAD 力图开发一个全自动的开源工具链,用于数字版图生成,遍及管芯,管壳,和电路板,最初注意力放在SoC设计的RIL-to-GDSII阶段。更详细地来说,我们的目标是以源码的形式发布一款可生成 tapeout 的工具,并且采取自由的协议,期望成为 EDA 界的 Linux ("Linux of EDA")

OpenROAD的方法寻求为EDA工具、学术-产业合作和学术研究本身建立一个新的范式。OpenROAD 的目的在于克服在EDA领域根深蒂固的 "culture", "critical mass / critical quality" 障碍, 建立开源的观念。本文的其余部分将简要介绍 OpenROAD的Alpha版本中的主要工具,以及从我们获得的经验教训。

2. 主要工具

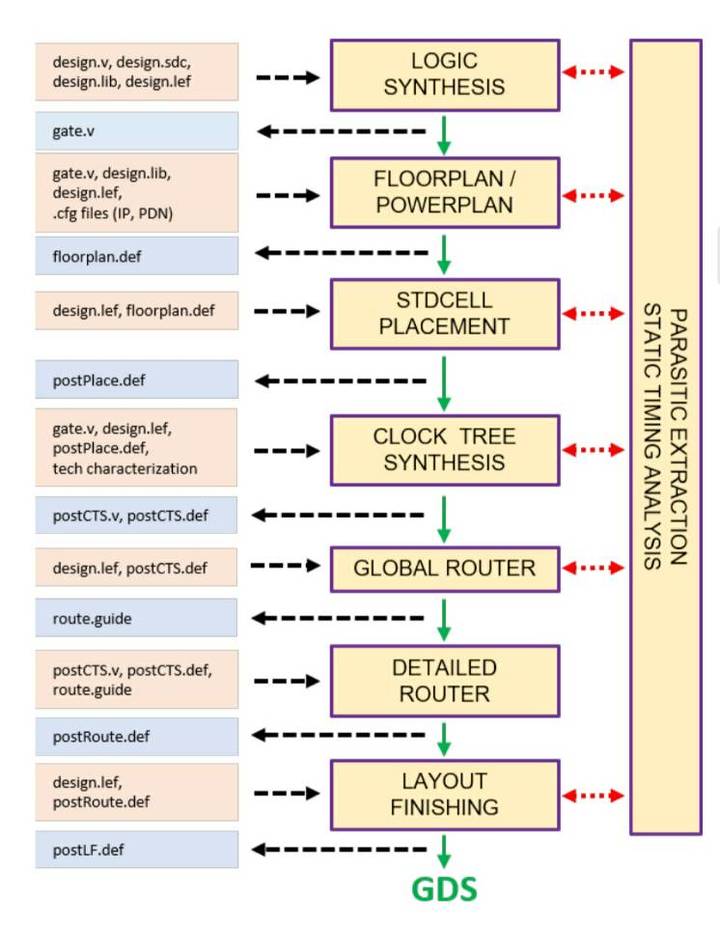

OpenROAD工具链由一组开源工具组成,这些工具将 RTL Verilog、constraints (.sdc)、liberty (.lib) 和 technology (.lef) 文件作为输入,目的是生成可用于流片的 GDSII 文件。图1说明了与单个OpenROAD任务对应的工具流。这些包括逻辑综合 (logic synthesis, LS),floorplan (FP) 和 power delivery network (PDN) ,布局,时钟树综合 (CTS),布线和版图生成。

图 1A. Logic Synthesis

开源LS的主要短板在于时序意识 (timing awareness) 和优化。Alpha版本对开源工具 YOSYS/ABC 进行了三个方面的改进。首先,我们使用强化学习技术 (reinforcement learning) 来实现时序驱动逻辑优化的自主空间探索设计。为了产生针对不同电路的最佳的综合脚本,我们开发了一个强化学习代理来自动一步一步地生成综合脚本,以满足目标时间约束,同时使总面积最小。其次,我们改进了ABC中的基本缓冲算法,并通过将 RePlAce 布局工具集成到逻辑综合流程中来实现物理感知 (physical-aware) 的缓冲和门尺寸,从而在门尺寸和缓冲中使用基于全局布局的线电容来评估改进的时序结果。第三,我们在流中增加了 SDC 常用命令子集。

B. Floorplan and PDN

Floorplan 和 PDN 由 TritonFPlan 完成,它有两个主要组成部分。第一个部分是宏封装,由 RePlAce 的混合尺寸(宏和标准单元格)全局布局和输入IO布局预置。宏封装使用基于 Parquet 的模拟退火算法 (simulated annealing, SA). SA 使用B*树表示宏布局,并具有双重目标标准,即最大化标准单元放置区域,同时最小化线长。SA解决方案把顶级PDN固定在合适位置,同时考虑诸如宏的特定光晕约束和垂直/水平通道宽度。从原始的混合尺寸全局布局创建多个平面图解决方案。 TritonFPlan的第二个组件遵循一种按安全构造 (safe-by-construction) 的方法,为每个宏封装方案创建了一个DRC正确的PDN。金属和通孔几何规则是从用户指定的配置文件中提取的。 RePlAce用于根据估计的总导线长度(包括放置的标准单元)来确定这些平面图(with PDN)解决方案中的最佳方案。目前仅支持矩形平面图。端帽 (endcap),tapcell 和 IO-pin 方法的实现正在进行中。

C. Placement and PDN refinement

RePlAce 是一款基于静电模拟的开源分析布局器,采用BSD协议。在OpenROAD中,RePlAce用于在 floorplanning 期间混合大小(宏和单元)布局基于开源工具的数据分析,用于在给定 floorplan 中的标准单元布局,以及在时钟树综合(CTS)期间用于时钟缓冲区合法化。时序驱动的 RePlAce 工具采用工业标准 LEF/DEF、Verilog、SDC 和 Liberty 格式进行输入。RePlAce 包含了 (1) 用于估算 Steiner 线长的 FLUTE;(2) 一种用于寄生参数估计的快速 RC 估计器;(3) 用于在布局期间静态时间分析的 OpenSTA. RePlAce 应用基于 OpenSTA 分析的信号网重加权 (reweighting) 迭代来改善时序。注意,RePlAce 当前不会改变逻辑综合 (LS) 提供的 netlist。

布局后,PDN 根据空间电流分布的评估做进一步改进。主要目标是 PDN 的单通道、正确和安全构造。floorplan 阶段 PDN在整个芯片中使用单个间距 (single patch),布局后,此 PDN 选择性地减值。芯片区域被平铺成区域,并且对于每个区域,选择一组已减填充的 PDN 布线模板。这些模板是可拼接的,因此它们在对接时遵守设计规则。PDN 工具将一组预定义的模板、用于早期设计的(floorplan 阶段)DEF 和可用的电源分析信息(例如,我们的 OpenSTA 工具可以提供基于实例的功率报告)作为输入。然后,训练过的卷积神经网络 (CNN) 为每个区域选择一个安全的模板。

D. Clock Tree Synthesis

TritonCTS基于GH-Tree(广义H-Tree)范式,对低功率、低偏移和低延迟时钟分布进行时钟树综合(CTS)。采用动态规划算法找到一个最小估计功率的时钟树拓扑结构,并且与给定的延迟和偏移目标一致。动态编程算法找到了具有最小估计功率的时钟树拓扑,且在给定的延迟时间和偏离目标之内。k-means算法适用于下沉聚类 (sink clustering)。TritonCTS 有与布局器器(RePlAce)的接口,用于插入时钟缓冲区合法化。

E. Global Routing

UTD-BoxRouter是BoxRouter 2.0 的修改版。该工具读取 LEF 和布局后的 DEF。它定义了称为 gcells 的全局布线单元,并执行全局布线以最小化单元内的拥塞和溢出,同时最小化线长和过孔 (vias)。 工具生成后续详细布线器执行所需的布线指导。 该全局布线器首先通过使用预布线,整数线性规划和基于协商的A *搜索 (negotiation-based A* search) 来确保布线稳定性,从而解决2D布线的问题。 该全局布线器使用已知的过孔和阻塞的整数线性编程算法,使用层分配 (layer assignment) 执行2D到3D映射。

F. Detailed Routing

TritonRoute 以 LEF 和 布局后的 DEF 作为输入,然后在给定全局布线解决方案的情况下,对信号网络和时钟网络进行详细的布线,以布线指南的格式进行。 在进行详细的布线之前,(1) TritonRoute使用广度优先搜索对全局布线解决方案进行预处理,以减少在保证网络连接性的情况下在稍后阶段产生环路的可能性;(2) TritonRoute通过考虑方向和走线轨迹偏移量来识别唯一实例,并以引脚访问模式来帮助连接到引脚。

该流程依次进行以下操作:轨迹分配和详细的布线阶段。首先,轨迹分配使用快速贪婪启发式方法 (fast greedy heuristic) 确定每个全局布线段的轨迹。 其次,基于片段的初始详细布线解决了多终端,多网络交换盒布线问题。 片段可以并行布线。 在每个片段中,使用多端子A *算法顺序布线网络。 第三,多次重复搜索和修改以减少线长和通孔数量,并提高 DRC 收敛性。

3. 分析工具

OpenROAD 在整个流程中使用了大量的分析工具和框架

A. Static Timing Analysis

OpenSTA 是商业 Parallax timer 的开源版本,采用 GPL3 协议。Paralla timer 引擎已商业性地提供近20年,并已被纳入许多的 EDA 和 IC公司的时序分析工具中。OpenSTA 在 GitHub 上开源。OpenSTA已经确认支持多个高级的 foundry nodes,并支持标准的时序报告样式

B. Parasitic Extraction

寄生参数提取(PEX)工具运行一个 foundry 的设计工具包(PDK),以建立线电阻、地电容和对同一层或上下相邻层线的耦合电容的线性回归模型。一个基本的用例是流程中的另一个工具(例如,CTS,全局布线,定时分析)调用PEX,提供一个由特定线路和它的邻近组成的输入DEF文件。提供的输出文件包括提取的寄生参数。预期的改进包括连接PEX功能到未来可能的广泛的 IDEA 物理设计数据库,并扩展模型拟合方法,以实现低开销的寄生参数估计器,用于时序驱动布局,在全局布线期间的串扰估计。

C. Cloud Infrastructure

为了让用户利用OpenROAD工具以及其他协作者开发的工具,云基础设施项目旨在提供端到端无缝的用户体验。在我们的云部署中,用户将他们的Git repo 预定到我们的云系统。设计更改推送到Git repo后,OpenROAD流程会自动编译,当流程完成时,用户会收到一封电子邮件通知。然后用户可以通过浏览器下载结果文件。如果需要,用户还可以在基于web的前端监控流程的进程。我们的云部署是弹性的,当更多的用户登录到服务时,或者当用户请求并行处理能力时,它会利用更多的计算资源。

D. Integration and Testing

上述的工具构成一个工具链,该工具链产生可用于产生准备最终验证和制造的设计。最初的支持平台是CentOS 6。。在这里,我们利用了一个基于现有设计的测试用例套件,这些设计之前已经准备好了,这些设计的复杂性和工艺都有。我们的测试用例套件还包括不断开发的顶尖复杂的SoCs。持续的集成测试套件在开发期间会分别验证这些工具,并记录回归指标和特性影响。

4. 未来主要的扩展

OpenROAD 项目的其他部分正在开发中,包括应用普适机器学习 (pervasive machine learning)在流程中进行优化,SoC 计划,芯片封装-PCB 协同设计 (chip-package-PCB co-design).

A. METRICS 2.0

为了使机器学习(ML)和最终自驱动的OpenROAD 流程的大规模应用成为可能,我们正在开发METRICS 2.0,它可以作为一个统一的、全面的设计数据收集和存储基础设施。METRICS 2.0 字典提供了一个标准化的度量标准列表,适合在工具或流程执行期间收集,以捕获关键设计参数以及设计流程中各种工具的结果。我们还提出了基于 JavaScript Object Notation (JSON) 的数据日志系统架构,以及基于MongoDB数据库的数据存储和指标检索系统架构。METRICS 2.0与TensorFlow等机器学习框架紧密结合,后者为MongoDB的读写提供了简单的接口,并支持机器学习算法的快速部署。采用机器学习算法得出的结果将被用于调整流程中工具的参数。

B. Early SoC Planning

为了缩短周转时间,我们计划以可靠的临时 floorplan 作为流程起点来启动OpenROAD工具链,以最大程度地减少运行失败的可能性。 可以通过在每个 IP 中嵌入物理实施信息(例如,使用在工业标准IP-XACT描述中的供应商扩展机制),以及通过使用特定技术和工具链的参数和统计模型,来增强SoC的早期布局规划评估。 结合这些信息可以进行早期区域和性能估算。

C. SoC-PCB

来源【首席数据官】,更多内容/合作请关注「辉声辉语」公众号,送10G营销资料!

版权声明:本文内容来源互联网整理,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 jkhui22@126.com举报,一经查实,本站将立刻删除。