答案对人有帮助,有参考价值

0

一个传输信道与一种业务类型相对应,在物理层,有时需要将不同的业务数据复接在一起,通过一个物理信道进行传输,这个过程就是物理层的业务复接。

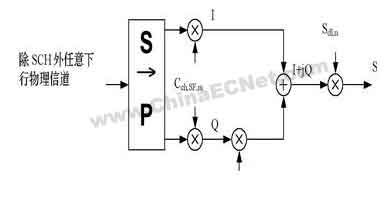

物理信道的扩频由两步组成。第一步是信道化,即将每个数据符号转化为多个码片, 以增加信号的带宽。每个数据符号内的码片数被称做扩频因子(SF);第二步为加扰,由此给扩频信号加扰。在下行链路中,两个连续符号组成的符号对经过串并变换,映射到I和Q支路上。映射的结果是偶数号和奇数号的符号分别映射到I和Q支路上。I 和 Q 支路由相同的实值信道化码Cch,SF,m扩频到码片速率,然后将I和Q支路上实值的码片序列变换成复值码片序列。该序列由复值的扰码Sdl,n加扰(复数相乘)。具体的扩频加扰框图(如图2所示)。

图 2 除SCH外所有下行物理信道的扩频

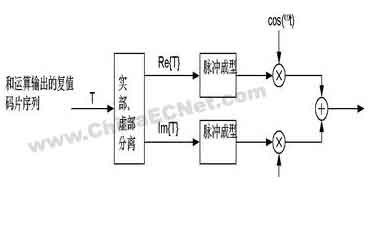

调制信号的码片速率为3.84 Mcps ,扩频过程产生的复值码片序列的调制为QPSK,具体的调制框图(如图3所示)。

图3 下行链路调制

实现方案

基带数据处理的电路结构

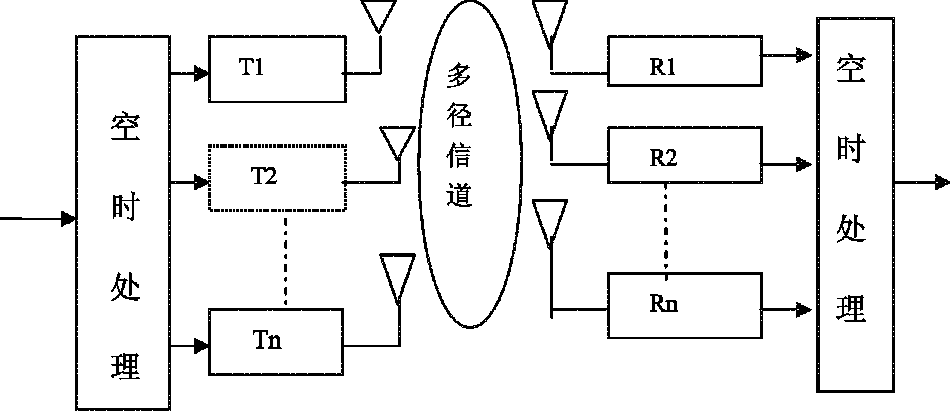

本文提出了“DSP+FPGA线性流水阵列结构”的实现方案:使用DSP与大规模FPGA协同处理基带发送数据。该处理单元以DPS芯片为核心,构造一个小的DSP系统,电路结构如图4所示。

在基带处理单元中,低层的信号预处理算法处理的数据量大wcdma始终同步对数据业务的影响,对处理速度的要求高,但运算结构相对比较简单,因而适于用FPGA进行硬件实现,这样能同时兼顾速度及灵活性。相比之下,高层处理算法的特点是所处理的数据量较低层算法少,但算法的控制结构复杂,适于用运算速度高、寻址方式灵活、通信机制强大的DSP芯片来实现。

在图4的电路结构中, DSP处理器利用其强大的I/O功能实现单元电路内部和各个单元之间的通信。从DSP的角度来看,可重构器件FPGA相当于它的协处理器。DSP通过本地总线对FPGA进行配置、参数设置及数据交互,实现软硬件之间的协同处理。DSP和FPGA各自带有RAM,用于存放处理过程所需要的数据及中间结果。除了DSP芯片和可重构器件FPGA外,硬件设计还包括一些外围的辅助电路,如FLASH EEPROM、外部存储器等。其中,FLASH EEPROM中存储了DSP的执行程序;外部存储器则作为FPGA的外部RAM扩展,用于存放数据处理过程中所需的映射图样。

基带处理单元的需求估计

基带处理单元的需求估计主要包含以下两个方面:

● 各个业务传输通道的数据处理: 以无线信道承载的最高业务速率384Kbps为例进行分析。根据3GPP协议TS25.211,为支持该种速率业务所要求的信道比特速率最大不超过960K(对应扩频增益SF=8,每10ms帧内的比特数是9600bits)。系统在1个10ms帧内所要处理的最大数据量为:

Wmax= 9600bits。

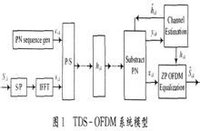

根据3GGP 协议TS 25.212 V2.2.0规定的下行数据基带处理流程(图1所示),并按固定位置复用的方式进行处理,每个数据比特须经过最多10个环节的处理过程,分别是:

估算平均每环节上每比特的处理要求8条指令。则10ms内必须完成的处理指令数是:9600×10×8=768000条。对应的处理能力要求是76.8MIPS。

● 消息处理:包含消息的解释、对应控制参数的计算、发给对应的处理FPGA。估计需求不超过一条承载64Kbps业务的无线信道的基带数据处理的需求。

综合考虑上述两个方面,则整个基带数据处理的等效需求是:

(9600+2400)×10×8/10ms=96MIPS

以TMS320C5410为例,其内部工作时钟频率高达100MHz,运算速度达100MIPS。基于C的软件开发环境和汇编级并行处理的优化程序,优化后的并行执行效率一般为80%,等效的处理能力为80MIPS。可见,若将整个基带数据处理交给该DSP芯片完成,其处理能力无法满足整个处理单元的需求。因此,在基带处理的实现方案

来源【首席数据官】,更多内容/合作请关注「辉声辉语」公众号,送10G营销资料!

版权声明:本文内容来源互联网整理,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 jkhui22@126.com举报,一经查实,本站将立刻删除。